- Home/

- GATE ELECTRONICS/

- GATE EC/

- Article

What is MOSFET?

By BYJU'S Exam Prep

Updated on: September 25th, 2023

MOSFET is among the most popular types of transistors due to their versatility and widespread use. MOSFET has wide applications for implementing digital design because of its higher integration density and relatively simpler manufacturing process. As a result, it is possible to economically realize 106-7 transistors on an integrated circuit.

Today’s field of microelectronics is dominated by a type of device called the metal-oxide-semiconductor field-effect transistor (MOSFET). Conceived in the 1930s but first realized in the 1960s, MOSFETs (also called MOS devices) offer unique properties that have led to the revolution of the semiconductor industry. This revolution has culminated in microprocessors having 100 million transistors, memory chips containing billions of transistors, and sophisticated communication circuits providing tremendous signal processing capability.

Download Formulas for GATE Electronics & Communication Engineering – Control System

Table of content

What is MOSFET?

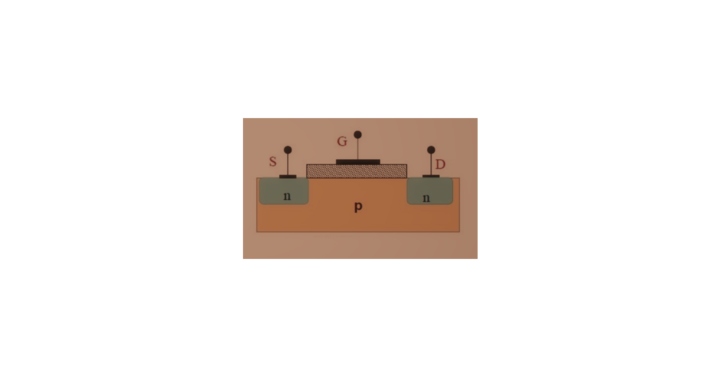

Metal Oxide Silicon Field Effect Transistors, known as MOSFETs, are electronic devices that switch or amplify circuits’ voltages. MOSFET is a current controlled device constructed by three terminals:

- Source(S),

- Drain(D), and

- Gate(G).

MOSFETs or Metal Oxide Silicon Field Effect Transistors were invented to overcome the disadvantages of FETs, such as slow operation, high drain resistance, and moderate input impedance.

Download Formulas for GATE Electronics & Communication Engineering – Digital Circuits

Full Form of MOSFET

The full form of MOSFET is Metal Oxide Silicon Field Effect Transistors.

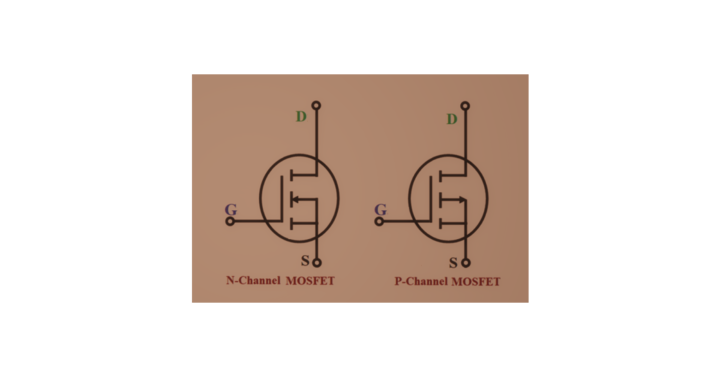

Symbols of MOSFET

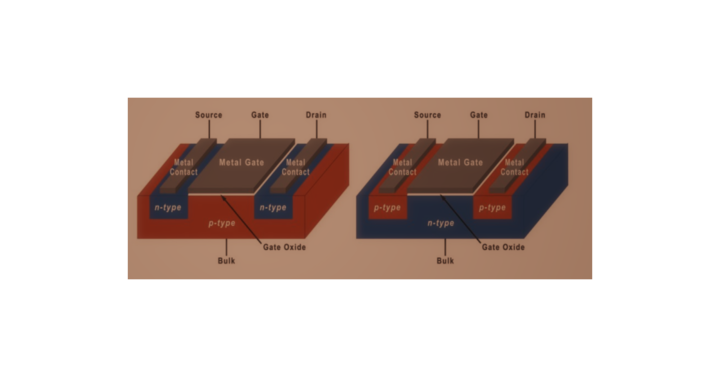

MOSFET is of two types, N-channel and P-channel MOSFET, available in depletion and enhancement mode. The following are the symbolic representation of the MOSFET for the N-Channel and P-channel.

We usually focus on enhancement mode MOSFET, where a channel between the source and drain has to be formed by applying different potentials at the gate terminal. In the case of depletion mode, a channel is readily available between the source and drain, which allows little flow of current, leading to power dissipation in the devices without applying any voltage between the terminal.

Download Formulas for GATE Electronics & Communication Engineering – Electronic Devices

Structure of MOSFET

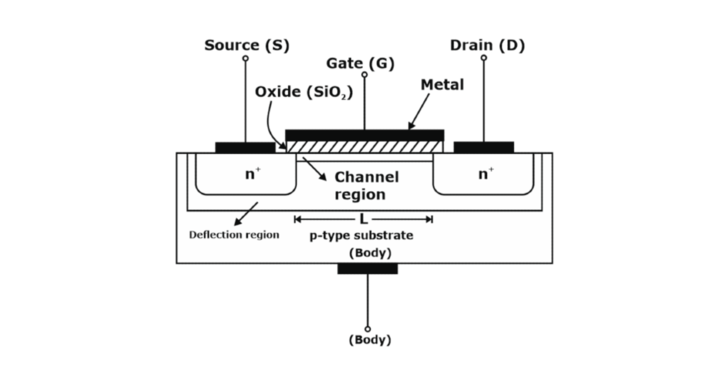

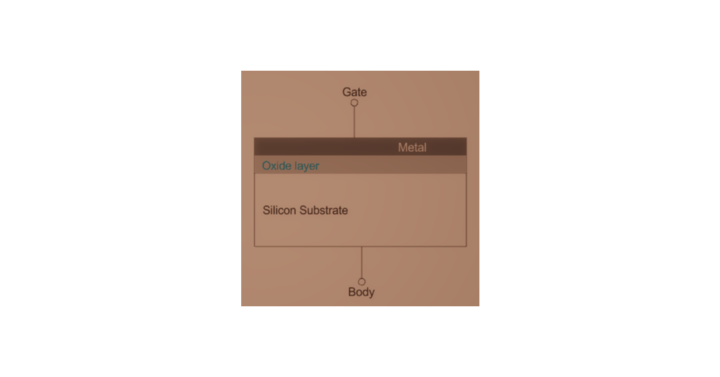

The MOS structure can be considered a parallel-plate capacitor, with the top plate being the positive plate, oxide being the dielectric, and Si substrate being the negative plate. (We are assuming P-substrate.) as shown below in Fig (a).

The MOSFET structure is shown in Fig. (b) as a candidate for an amplifying device.

Called the “gate” (G), the top conductive plate resides on a thin dielectric (insulator) layer, which itself is deposited on the underlying p-type silicon “substrate.” To allow current flow through the silicon material, two contacts are attached to the substrate through two heavily-doped n-type regions because the direct connection of metal to the substrate would not produce a good “ohmic” contact. These two terminals are called “source” (S) and “drain” (D) to indicate that the former can provide charge carriers and the latter can absorb them. Fig. (c) represents the side view of the MOSFET structure.

In the MOSFET, the gate plate must serve as a good conductor and be realized by metal(aluminum) in early generations of MOS technology. However, it was discovered that non-crystalline silicon (“polysilicon” or simply “poly”) with heavy doping (for low resistivity) exhibits better fabrication and physical properties. Thus, today’s MOSFETs employ polysilicon gates. The MOSFET device is symmetric, so either n+ regions can be the source or drain.

Biasing Method of MOSFET

There are four biasing methods for MOSFET: –

- Drain to Gate bias

- Voltage divider bias

- Fixed bias

- Self-bias

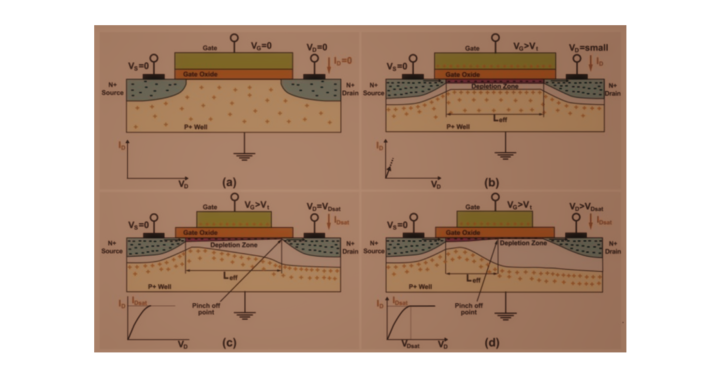

Formation of Channel in the MOSFET

First, the holes are repelled by the positive gate voltage, leaving behind negative ions and forming a depletion region. Next, electrons are attracted to the interface, creating a channel (“inversion layer”). The following figure shows how the channel is formed in the MOSFET when we apply the positive voltage at the gate terminal of the MOSFET.

Operating Condition for MOSFET

Various MOSFETs can be used for various purposes depending upon the operating condition. The operating condition of various MOSFETs are explained below:

Operating Condition for N channel Enhancement Type MOSFET

|

Operating region |

Required condition |

|

Cut off region |

VGS < VTN |

|

Triode region |

VGS > VTN, VDS < VDS(sat) (or) VDS < VGS – VTN |

|

Saturation region |

VGS > VTN, VDS > VDS(sat) (or) VDS > VGS –VTN |

Operating Condition for P Channel Enhancement Type MOSFET

|

Operating region |

Required condition |

|

Cut off region |

VSG < |VTP| |

|

Triode region |

VSG > |VTP|, VSD < VSD(sat) or VSD < VSG + VTP |

|

Saturation region |

VSG > |VTP|, VSD > VSD (sat) or VSD > VSG + VTP |

Operating Condition for N Channel Depletion Type MOSFET

|

Operating region |

Required condition |

|

Cut off region |

VGS < VTN |

|

Triode region |

VGS > VTN, VDS < VDS(sat) (or) VDS < VGS – VTN |

|

Saturation region |

VGS > VTN, VDS > VDS(sat) (or) VDS > VGS – VTN |

Operating Condition for P Channel Depletion Type MOSFET

|

Operating region |

Required condition |

|

Cutoff region |

VSG < VTP |

|

Triode region |

VSG > VTP, VSD < VSD(sat) (or) VSD < VSG + VTP |

|

Saturation region |

VSG > |VTP|, VSD > VSD(sat) (or) VSG + VTP |

If you are preparing for GATE and ESE, avail Online Classroom Program to get unlimited access to all the live structured courses and mock tests from the following link: