Structural Hazard: Definition, Example

By BYJU'S Exam Prep

Updated on: September 25th, 2023

A structural hazard arises when two (or more) pipelined instructions need the same resource. Instructions must therefore be carried out in series rather than parallel for a segment of the pipeline. On occasion, resource hazards are regarded as structural dangers. Here we have discussed the structural hazards in detail.

According to the GATE CSE Syllabus, structural hazard is one of the most important topics. Read more about the structural hazard in pipelining along with its examples in the upcoming sections.

Download Formulas for GATE Computer Science Engineering – Algorithms

Table of content

What are Structural Hazards?

Structural hazard is one of the three hazards in the pipeline. A structural hazard is caused due to resource conflict in the pipeline stage. When two different instructions access the same resource in the same stage, this situation is termed a structural hazard.

These structural hazards cause stalls in the pipeline. To minimize or eliminate the stalls due to the structural dependency in the pipeline, we use a hardware mechanism called the Renaming technique.

Structural Hazards in Pipelining

A cycle in the pipeline without new input initiation is called an extra cycle, also called a stall or hazard. When a stall is present in the pipeline, then CPI (Cycle per Instruction) ≠ 1. There are three types of hazards possible in the pipeline, namely:

- Structural Hazards

- Data Hazards

- Control Hazards

A structural dependency causes a structural hazard in pipelining. This dependency occurs due to resource conflict. A resource may be a memory or register or a functional unit like ALU (Arithmetic Logical Unit) in the CPU. In simple words, when different instructions collide while trying to access the same resource in the same segment of the pipeline, then it causes a structural hazard.

Handling Structural Hazards in Pipelining

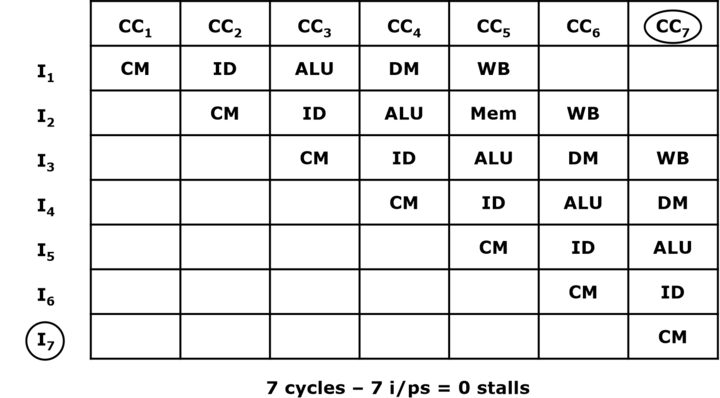

The structural hazards are minimized using a hardware technique is used called renaming. The renaming mechanism states that it splits the memory into two independent sub-modules to store instruction and data separately. The module used to store instruction is called code memory (CM), and the module used to store data is called data memory(DM).

In this technique, as we proceed further, we refer to the code memory in the first stage and refer to the data memory next, so accessing these two memories in the same cycle does not create any conflict or hazard. In this manner, we eliminate structural hazards in pipelining.

Structural Hazard Example

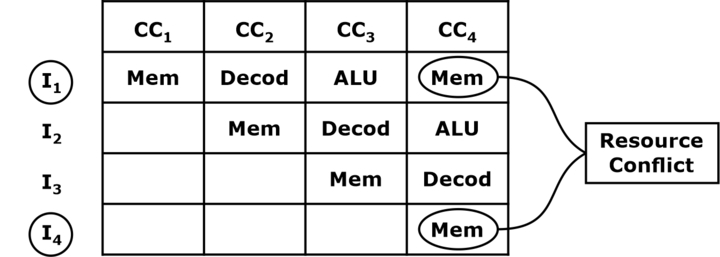

Let us understand the structural hazard through an example. Consider we have four instructions, I1, I2, I3, and I4, accessing Memory (Mem), Instruction Decode (Decod), and ALU stages of the pipeline as shown in the figure below:

In the above execution sequence instructions, I1 and I4 both are trying to access the same resource, which is Mem (Memory) in the same CC4(Clock Cycle – 4). This situation in the pipeline is called a structural hazard.

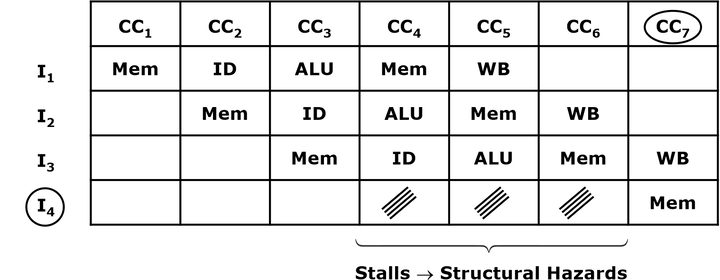

Conflict is an unsuccessful operation, so to handle this problem, we need to stop the I4 instruction fetch from the memory until the resource becomes available. This waiting creates stalls in the pipeline, as shown in the below figure:

In the cycle diagram, instruction I1 refers to the memory in the fourth stage to read or write the data. Simultaneously, instruction I4 refers to the memory in the first stage of the pipeline to access data in the same cycle CC4. This situation has resulted in conflict. Now to eliminate this, we will use the renaming technique. That is, we divide the memory into two modules, code memory(CM) and data memory (DM), and refer to the CM in the first stage to read data and refer to DM in the fourth stage to write data. This implementation is shown in the below figure:

Using the renaming technique to overcome the structural hazard, we achieve pipeline CPI=1 with 0(zero) stalls.