Time Left - 15:00 mins

GATE 2024 Subject Name Foundation Quiz 91

Attempt now to get your rank among 34 students!

Question 1

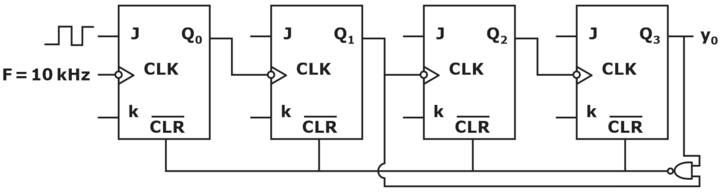

In the following figure, the J and K inputs of all the four Flip-Flops are made high. The frequency of the signal at output Y0 is

Question 2

A 3 bit module-8 ripple counter uses JK flip-flop. If the propagation delay of each FF is 40ns, the maximum clock frequency that can be used is equal to

Question 3

DRAMs consist of

Question 4

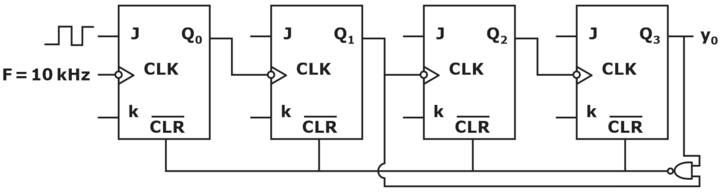

A 4-bit shift register circuit configured for right-shift operation,

, is shown. If the present state of the shift register is ABCD = 1101, the number of clock cycles required to reach the state ABCD = 1111 is _________.

, is shown. If the present state of the shift register is ABCD = 1101, the number of clock cycles required to reach the state ABCD = 1111 is _________.

Question 5

Find size of ROM (in bits) to implement Dual 4 – line to 1 – line MUX with common selection inputs

- 34 attempts

- 0 upvotes

- 0 comments

Jun 12ESE & GATE EC