Time Left - 15:00 mins

GATE 2019: Digital Circuits Rapid Quiz 3

Attempt now to get your rank among 878 students!

Question 1

The minimum number of 2 to 1 multiplexers required to realize a 4 to 1 multiplexer is

Question 2

A finite state machine M, is constructed by connecting output of a 3-state, finite state machine to inputs of a 9-state, finite state machine. M is reimplemented using a state register with the minimum number of bits. The minimum number of bits in state register is _____.

Question 3

Consider the circuit given below

MSB and LSB of MOD 10 ripple up counter acts as clock to 4 bit ripple down and up counter respectively.

Initially, all the counter were cleared and output of comparator was A = B. The clock pulse is applied. The minimum number of clock pulses required to make A = B again are

Question 4

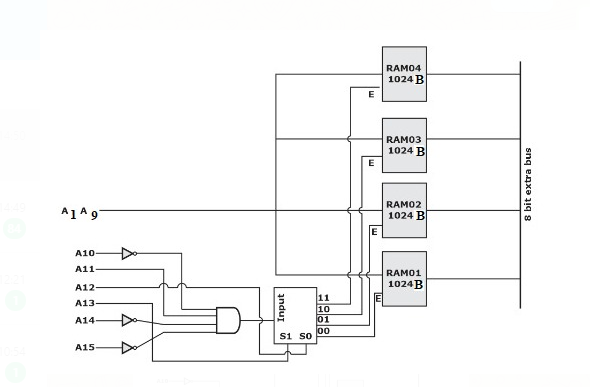

There are four chips each of 1024 bytes connected to a 16 bit address bus address bus as shown in the figure below. RAMs, 1, 2, 3, and 4 respectively are mapped to addresses

Question 5

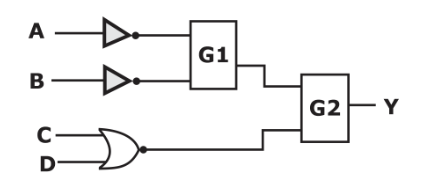

In the figure shown, the output Y is required to be Y = AB +  . The gates G1 and G2 must be, respectively,

. The gates G1 and G2 must be, respectively,

Question 6

Consider a four bit D to A converter. The analog value corresponding to digital signals of values 0000 and 0001 are 0 V and 0.0625 V respectively. The analog value (in Volts) corresponding to the digital signal 1111 is ________.

- 878 attempts

- 1 upvote

- 8 comments

Jul 20ESE & GATE EC