Time Left - 40:00 mins

GATE EE : Digital Electronics - National Champion Test

Attempt now to get your rank among 617 students!

Question 1

An input device is interfaced with Intel 8085A microprocessor as memory mapped I/O. The address of the device is 2500H. In order to input data from the device to accumulator, the sequence of instructions will be

Question 2

Which one of the following is not a vectored interrupt?

Question 3

Which of the following statement is Incorrect for the range of n bits binary numbers

Question 4

The frequency of the clock signal applied to the rising edge triggered D flip-flop shown in the following figure is 10 kHz. The frequency of the signal available at Q is

Question 5

The digital circuit shown in the following figure works as a

Question 6

The digital circuit using two inverters shown in figure will act as

Question 7

If F = X'YZ + XZ, then what will be the minimum number of literals?

Question 8

Decimal 43 in Hexadecimal and BCD number system is respectively

Question 9

The number of product terms in the minimized sum-of-product expression obtained through the following K-map is (where “d” denotes don’t care states)

Question 10

In an 8085 microprocessor, the shift registers which store the result of an addition and the overflow bit are, respectively

Question 11

Following is the segment of a 8085 assembly language program:

On completion of RET execution, the contents of SP is:

On completion of RET execution, the contents of SP is:

Question 12

11001, 1001 and 111001 correspond to the 2’s complement representation of which one of the following sets of number?

Question 13

The present output Qn of an edge triggered JK flip-flop is logic 0. If J=1, then Qn +1

Question 14

The figure shows a binary counter with synchronous clear input. With the decoding log shown, the counter works as a

Question 15

The Boolean function f implemented in figure using two input multiplexers is

Question 16

If P, Q, R are Boolean variables, then  simplifies to

simplifies to

Question 17

All the logic gates shown in the figure have a propagation delay of 20 ns. Let A = C = 0 and B = 1 until time t = 0. At t = 0, all the inputs flip (i.e., A = C = 1 and B = 0) and remain in that state. For t > 0, output Z = 1 for a duration (in ns) of _________.

Question 18

A 4-bit D/A converter is connected to a free-running 3-bit UP counter, as shown in the following figure. Which of the following waveforms will be observed at V0?

In the figure shown above, the ground has been shown by the symbol

In the figure shown above, the ground has been shown by the symbol

Question 19

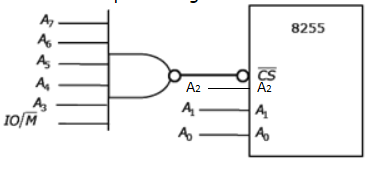

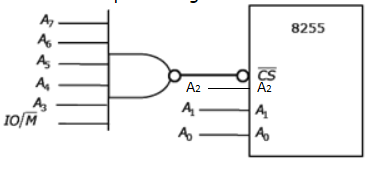

An 8255 chip is interfaced to an 8085 Microprocessorsystem as an I/O mapped I/O as shown in the figure. The address lines A0 and A1 of the 8085 are used by the 8255 chip to decode internally its three ports and the Control register. The address lines A3 to A7 as well as the IO/ signal are used for address decoding. The range of addresses for which the 8255 chip would get selected is:

signal are used for address decoding. The range of addresses for which the 8255 chip would get selected is:

Question 20

The circuit shown consists of J-K flip-flops, each with an active low asynchronous reset  . The counter corresponding to this circuit is

. The counter corresponding to this circuit is

- 617 attempts

- 6 upvotes

- 22 comments

Jun 4ESE & GATE EE