Time Left - 12:00 mins

BARC 2020: Nuclear Quiz 3

Attempt now to get your rank among 691 students!

Question 1

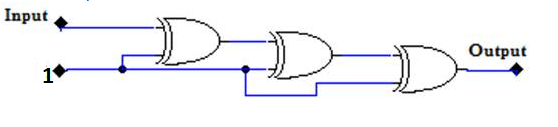

Consider the circuit given below

Assuming the initial value of counter output (Q1, Qo) as zero, the counter output for 8 clock pulses in decimal form is

Assuming the initial value of counter output (Q1, Qo) as zero, the counter output for 8 clock pulses in decimal form is

Question 2

Consider the CMOS logic circuit shown in the figure :

The logic implemented by this circuit is (the input is either O or – VDD).

Question 3

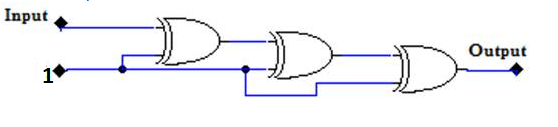

The ‘I’ input of the following circuit is high. If we apply 01101011 at the other input (first bit 0).

Find the output.

Find the output.

Question 4

In the following figure, the J and K inputs of all the four Flip-Flops are made high. The frequency of the signal at output Y is

Question 5

The I/P – O/P voltage for the standard TTL family are given by  = 2.6 V

= 2.6 V  = 0.6V

= 0.6V  = 2V and

= 2V and  = 0.4 V. The maximum- amplitude noise that can be tolerated when a low O/P is driving an input is

= 0.4 V. The maximum- amplitude noise that can be tolerated when a low O/P is driving an input is

Question 6

Given that:

The radix 8’s complement of Y is

The radix 8’s complement of Y is

Question 7

Find the correct minimized expression Y (A, B, C, D) = ∑m (0, 3, 7, 13, 14) + ∑d (1, 2, 12).

Question 8

Let r denote number system radix. The only value(s) of r that satisfy the equation √121 = 11 is/are

Question 9

A 4-bit shift register circuit configured for right-shift operation,

, is shown. If the present state of the shift register is ABCD = 1101, the number of clock cycles required to reach the state ABCD = 1111 is _________.

, is shown. If the present state of the shift register is ABCD = 1101, the number of clock cycles required to reach the state ABCD = 1111 is _________.

Question 10

consider the following circuits (assume all gates have a finite propagation delay)

1)

2)

3)

4)

Which of these circuits generate a periodic square wave output?

1)

2)

3)

4)

Which of these circuits generate a periodic square wave output?

- 691 attempts

- 1 upvote

- 6 comments

Jun 15ESE & GATE EC