Time Left - 15:00 mins

GATE 2024 Networks Rank Booster Quiz 3

Attempt now to get your rank among 17 students!

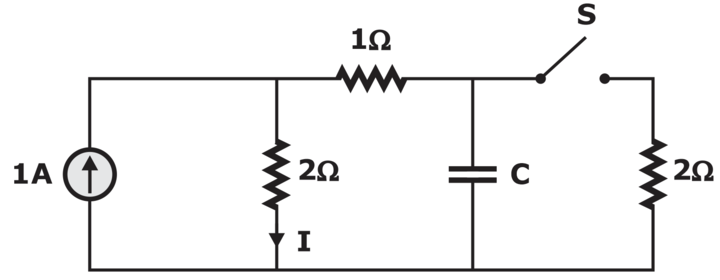

Question 1

The steady state in the circuit, shown below is reached with S open. Now S is closed at . The current I at

. The current I at is _________A

is _________A

Question 2

The circuit shown in figure is supplied by a dc source. The switch (S) in the circuit is closed at t = 0 and remains closed for a long time.

The steady state output voltage (V0) is ________V.

Question 3

It is given that series voltage

The value of Vc at t = 0+ sec is _______V.

Question 4

In the RL circuit shown below, switch (s.w) is in position 1 long enough to establish steady state conditions, and at t = 0 it is switched to position 2. Find the resulting current

Question 5

If and the switching is done at

and the switching is done at , find

, find for

for if the initial capacitor voltage be 2V.

if the initial capacitor voltage be 2V.

Question 6

Consider the following network

The value of ![]() at t = 0+ is

at t = 0+ is

Question 7

Consider the circuit shown in figure.

If a unit ramp input Vi(t) is applied, then the steady state output voltage ‘V0’ is

- 17 attempts

- 0 upvotes

- 0 comments

Nov 8ESE & GATE EC