Classroom

# ESE Mains Achiever's Study Plan

**Electronics & Communication Engineering**

**Analog Circuits Part-1**

Prep Smart. Score Better. Go gradeup

www.gradeup.co

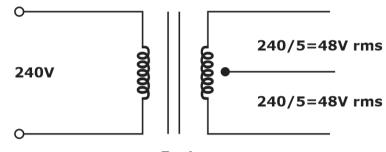

- **1.** A full wave rectifier has load resistance of 500  $\Omega$  and the used diodes has internal resistance of 50  $\Omega$ . If turn ratio from primary to half of secondary of transformer is 5:1 and primary winding voltage is 240 V rms, 50 Hz then calculate:

- (i) dc and ac output current

- (ii) dc and ac output voltage

- (iii) dc diode voltage and current

- (iv) efficiency and regulation factor

- (v) PIV and ripple frequency

- (vi) RMS output current

#### Sol.

R<sub>L</sub> = 500 Ω, R<sub>f</sub> = 50 Ω

Rms secondary voltage =

$$\frac{V_m}{\sqrt{2}}$$

= 48

$\Rightarrow V_m = 48\sqrt{2} = 67.88V$

$\therefore I_m = \frac{V_m}{R_f + R_L} = \frac{67.88}{550} = 123 \text{ mA}$

(i)  $I_{DC} = \frac{2I_m}{\pi} = \frac{2 \times 123}{\pi} = 78.3 \text{ mA}$

AC output current I'rsm ,

So, I'rms = r × I<sub>DC</sub> = 0.483 × 78.3

I'rms = 37.82 mA

(ii) V<sub>DC</sub> = I<sub>DC</sub>, R<sub>L</sub> = 78.3 × 10<sup>-3</sup> × 500 = 39.15 V

AC output voltage V'rms = r . V<sub>DC</sub>

= 0.483 × 39.15

V'rms = 18.9 V

(iii)  $V_{\text{diode,DC}} = -\frac{2V_m}{\pi} = -\frac{2 \times 67.88}{\pi} = -43.16V$

$I_{\text{diode, DC}} = \frac{I_m}{\pi} = 39.15 \text{ mA}$

### Vision 2021 Batch-3

A Course for ESE & GATE Electronics Aspirants

(iv)

$$\%\eta = 81 \times \frac{R_L}{R_f \times R_L} = 81 \times \frac{500}{550}\%$$

$\%\eta = 73.63\%$

$\% \text{Regulation} = \frac{R}{R_L} \times 100\% = \frac{50}{500} \times 100\% = 10\%$

(v) PIV = Vm

= 2 × 67.88 = 135.76 V

Ripple frequency = 2 f<sub>0</sub> = 100 Hz

(vi) RMS output current

$I_{\text{rms}} = \frac{I_m}{\sqrt{2}} = \frac{123}{\sqrt{2}} \text{mA}$

$$\Rightarrow I_{\text{rms}} = 86.97 \text{ mA}$$

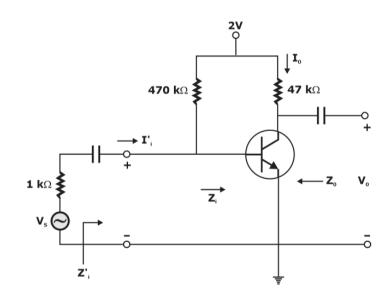

**2.** For the network shown below, determine the value of following parameters by using complete hybrid-equivalent model.

A.  $Z_i \mbox{ and } Z^\prime_i$

B. Av

C.

$$A_i = \frac{I_o}{I_i}$$

and  $A'_i = \frac{I_o}{I'_i}$

$D. Z_{o}$

The h-parameters of the transistor are:

$h_{fe}$  = 110 ;  $h_{ie}$  = 1.6  $k\Omega$

$h_{fe}$  = 2  $\times$  10  $^{-4}$ ;  $h_{oe}$  = 20  $\mu \, \mho$

## Vision 2021 Batch-3

A Course for ESE & GATE Electronics Aspirants

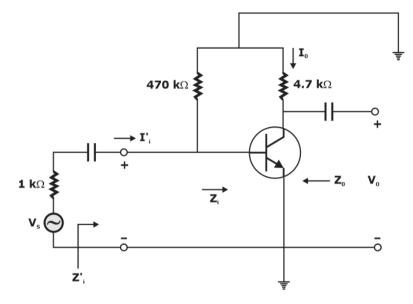

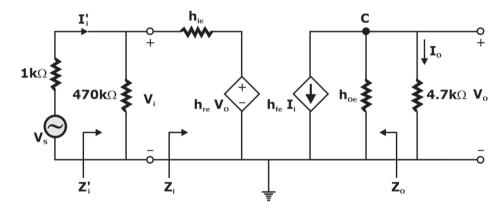

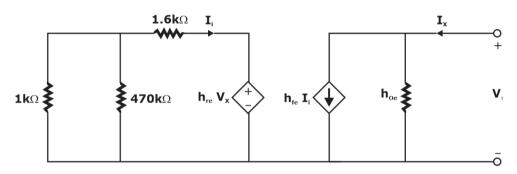

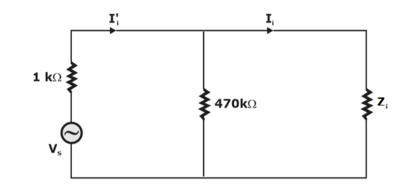

#### Sol. Redrawing the AC equivalent circuit

Substituting h-parameter equivalent circuit:

Current gain (A<sub>i</sub>):

$$\begin{split} &I_{o} \frac{+h_{fe}I_{i} \frac{1}{h_{o}}}{\frac{1}{h_{oe}} + 4.7 \, k \, \Omega} \\ & \Longrightarrow \frac{I_{o}}{I_{i}} = A_{i} \frac{+h_{fe}}{1 + h_{oe} \times 4.7 k \Omega} = \frac{+110}{1 + 20 \times 10^{-6} \times 4.7 \times 10^{3}} \\ & \Rightarrow A_{i} = \frac{110}{1 + 0.094} = 100.548 \end{split}$$

#### Input impedance (Z<sub>i</sub>):

Applying KVL in input loop

$$\begin{split} V_{i} &= h_{i}I_{i} + h_{re}V_{o} = h_{re}V_{o} = h_{i}I_{i} + h_{re}\times \left(I_{0}\times4.7k\Omega\right) \\ &= h_{i}I_{i} - h_{re}\left(+4.7k\Omega\right)A_{i}\ I_{i} \end{split}$$

### Vision 2021 Batch-3

A Course for ESE & GATE Electronics Aspirants

$$\begin{split} \frac{V_i}{I_i} &= Z_i = h_i - h_{re} \times 4.7 \times 10^3 \times 100.548 \\ &= 1600 - 2 \times 10^{-4} \times 4.7 \times 10^3 \times 100.548 \end{split}$$

$Z_i = 1.5 \text{ k} \Omega$

Voltage gain (A<sub>v</sub>):

$$\begin{split} A_{v} &= \frac{V_{o}}{V_{i}} = \frac{I_{o} \times 4.7}{V_{i}} = \frac{A_{i}I_{i} \times 4.7}{V_{i}} \\ &= \frac{A_{i} \times 4.7}{Z_{i}} = \frac{100.548 \times 4.7}{1.5} \end{split}$$

#### Output impedance (Z<sub>o</sub>):

Step 1: Disable external sources present in the input.

Step 2: Disconnect load resistance RL form output circuit.

Step 3 : Assume that voltage  $V_x$  is applied at output port and current  $I_x$  is flowing into output node then  $R_0$  is calculated as  $V_x/I_x$ .

#### KCL at output node

$$\begin{split} &I_x = h_o \; V_x + \; h_f \; I_i \\ \Rightarrow \frac{I_x}{V_x} = h_o + h_f . \frac{I_i}{V_x} \\ &\frac{1}{Z_o} = \frac{I_x}{V_x} = h_o + h_f . \frac{I_i}{V_x} \; \dots \dots (i) \\ &\text{KVL in input loop} \\ &I_i \; (1 k \Omega \; || \; 470 \; k \Omega) \; + \; 1.6 \; k \Omega \; I_i + \; h_r \; V_x = 0 \\ &\rightarrow 0.9978 \; I_i \; + \; 1.6 \; I_i = \; h_r \; V_x \end{split}$$

$$\Rightarrow \frac{I_{i}}{V_{x}} = \frac{2}{2.56k\Omega} = \frac{2 \times 10^{-4}}{2.56 \times 10^{3}}$$

Now  $\frac{1}{Z_{o}} = 20 \times 10^{-6} + 110 \times \frac{2 \times 10^{-4}}{2.56 \times 10^{3}}$

### Vision 2021 Batch-3

A Course for ESE & GATE Electronics Aspirants

$$\begin{aligned} \frac{1}{Z_o} &= 2.86 \times 10^{-5} \\ \therefore Z_o &= 34.97 \, \text{k}\Omega \simeq 35 \text{k}\Omega \\ Z'_i &: Z'_i &= 470 \, \text{k}\Omega \mid \mid Z_i = \frac{470 \times 1.5}{470 + 1.5} = 1.495 \text{k}\Omega \\ A'_i &: A'_i = \frac{I_0}{I_i} = \frac{I_o}{I_i} \cdot \frac{I_i}{I_i} = A_i \frac{I_i}{I_i'} \\ I_i &= I'_i \frac{470 \text{k}\Omega}{Z_i + 470 \text{k}\Omega} \\ \Rightarrow \frac{I_i}{I_i'} &= \frac{470 \text{k}\Omega}{1.5 \text{k}\Omega + 470 \text{k}\Omega} = 0.9968 \\ \therefore A'_i &= 100.548 \times 0.9968 \\ A'_i &= 100.226 \end{aligned}$$

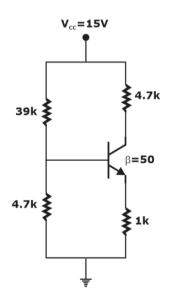

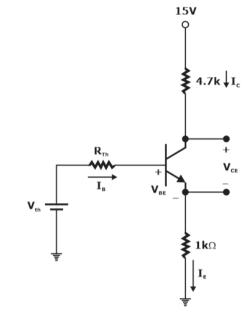

**3.** For the circuit shown in figure,

(i) Determine the operating point

(ii) Find the stability factor. Given:  $V_{BE}$  = 0.6 V,  $\beta$  = 50

## Vision 2021 Batch-3

A Course for ESE & GATE Electronics Aspirants

$V_{Th} = \frac{47k\Omega \times 15V}{39k\Omega + 47k\Omega} = 1.61327 V \dots (1)$   $R_{Th} = 4.7 k\Omega || 39 k\Omega = 4.1945 k\Omega \dots (2)$ (i) Step (1): KVL for input section  $V_{TH} - I_B R_{Th} - V_{BE} - (I_E \times 1 k \Omega) = 0 \dots (3)$   $\rightarrow (I_B \times 4.195k\Omega) + ((1+\beta)I_B \times 1k\Omega) - 1.61327V - 0.6V \dots (4)$   $\Rightarrow I_B = \frac{1.01327V}{4.1945k + 5K} = \frac{1.01327V}{55.1945k} \dots (5)$   $\therefore I_{CQ} = \beta I_B = 50 \times 0.018358 mA$   $= 0.1979 mA \dots (6)$ Step (2): KVL for output section  $15V - (4.7k\Omega \times I_c) - V_{CE} - (1k\Omega \times I_E) = 0 \dots (7)$   $V_{CE} = 15V - (4.7k\Omega \times 0.9179 mA) - 1k\Omega (\frac{1+\beta}{\beta})I_c \dots (8)$   $= 15V - 4.31413V - 0.936258V \dots (9)$   $\therefore V_{CEQ} = 9.7496 V \dots (10)$   $\therefore Q = (9.7496 V, 9.9176 mA) \dots (11)$ (ii) Stability factor,  $S = \frac{\partial I_C}{\partial I_{C_0}}$

In self bias arrangement, stability factor,

$$S = \frac{1+\beta}{1+\beta \left[\frac{R_{E}}{R_{E}+R_{Th}}\right]} \dots (1)$$

Vision 2021 Batch-3 A Course for ESE & GATE Electronics Aspirants

$$\Rightarrow S = \frac{1+50}{1+50\left(\frac{1K}{1K+4.1945k}\right)} \qquad ......(2)$$

$$= \frac{51}{1+50(0.1925)} = \frac{51}{1+9.625} \qquad .....(2)$$

$$\therefore S = 4.8 \dots (3)$$

$$V_{Th} = \frac{R_2 V_{CC}}{R_1 + R_2} = \frac{5k\Omega \times 3V}{5k\Omega + 5k\Omega} = 1.5V \dots (1)$$

$$R_{Th} = R_1 ||R_2 = 5 k\Omega || 5 k\Omega = 2.5 k\Omega \dots (2)$$

$$Step (1): KVL \text{ for base-emitter loop}$$

$$V_{th} - I_B R_{th} - V_{BE} - (1 + \beta) I_B \times 1 k \Omega = 0 \dots (3)$$

$$I_B = \frac{1.5V - 0.7V}{2.5k\Omega + (5 \times 1k\Omega)} = \frac{0.8V}{47.5k\Omega} = 0.016842\text{mA} \dots (4)$$

$$\therefore I_{CQ} = \beta I_B = 0.741 \text{ mA} \dots (5)$$

$$Step (2): KVL \text{ for output section}$$

$$3V - V_{CEQ} - (I_E \times 1k \Omega) = 0 \dots (6)$$

$$V_{CEO} = 3V - (1 + \beta) I_B \times 1 k \Omega \dots (7)$$

$$= 3V - 0.75789 V \dots (8)$$

$$\therefore V_{CEO} = 2.24211 V \dots (9)$$

$$\therefore Q = [2.24211V, 0.741 \text{ mA}] \dots (10)$$

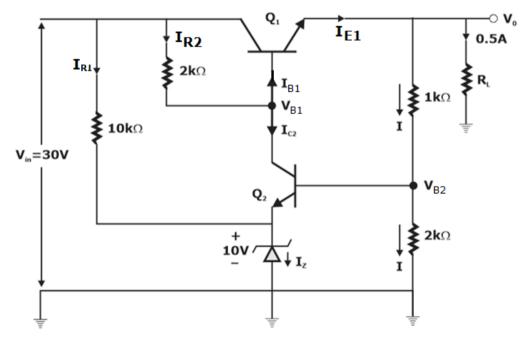

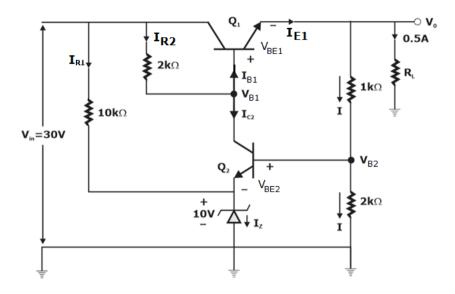

4. Find the various voltages and current in the regulator circuit. Find the power dissipation in the Zener and transistor  $Q_1$

### Vision 2021 Batch-3

A Course for ESE & GATE Electronics Aspirants

#### Sol.

Form the figure it is clear that

$$\begin{split} V_{B_2} &= V_Z + V_{BE_2} = 10V + 0.7 = 10.7V \\ \therefore I = \frac{V_{B_2}}{2k} = \frac{10.7}{2k} = 5.35 \text{ mA} \end{split}$$

Here the  $\beta$  is not given. Assume high value of  $\beta$  that implies base current can almost be neglected

$$\therefore I = 5.35 \text{ mA}$$

$$\therefore V_0 = I \times [1k + 2k] = 3k \times 5.35 \text{ m} = 16.05V$$

$$\therefore R_L = \frac{16.05}{0.5} = 32.1\Omega$$

From the fig

$$V_{B_1} = V_0 + V_{BE_1}$$

$$= 16.05 + 0.7 = 16.75 \text{ V}$$

$$\therefore I_{R_2} = \frac{V_{in} - V_{B_1}}{2k}$$

$$= \frac{30 - 16.75}{2k}$$

$$= \frac{13.25}{2k} = 6.625 \text{ mA}$$

$$I_{R_1} = \frac{V_{in} - V_Z}{10k}$$

$$= \frac{30 - 10}{10k} = \frac{20}{10k} = 2\text{mA}$$

# Vision 2021 Batch-3

A Course for ESE & GATE Electronics Aspirants

As  $\beta$  is very high  $I_{_{B_{\star}}} \approx 0A$  $I_{C_{2}} = I_{R_{2}} = 6.625 \,\text{mA}$  $\therefore I_{C_2} = I_{E_2} = 6.25 \text{ mA}$  $\therefore \, I_{_{Z}} \, = \, I_{_{E_{_{2}}}} \, + \, I_{_{R_{_{1}}}} \, = 2mA + 6.625\, mA$ = 8.625 mA From the figure, KCL at output node  $I_{_{\!\!F_{\!-}}} = I + I_{_{\!\!1}} = 5.35 mA + 0.5 A$ = 0.50535 A  $\beta$  is very high  $I_{\text{B}_{1}}\approx 0 \Longrightarrow I_{\text{E}_{1}}=I_{\text{C}_{1}}=0.50535\text{A}$ Power dissipation in the zener diode:  $P = V_Z \times I_Z$  $P = 10 \times 8.625 \text{ mA}$ P = 86.25 MwPower dissipation in the transistor Q<sub>1</sub>:  $P = V_{CE1} \times I_{C1}$  $\mathsf{P} = \left(\mathsf{V}_{\mathsf{C}_1} - \mathsf{V}_{\mathsf{E}_1}\right) \times \mathbf{I}_{\mathsf{C}_1}$

$P = (30 - 16.05) \times 0.50535$ P = 7.049 W

**5.** What is meant by feedback. Write a short note on negative feedback & mention it's advantages & disadvantages.

#### Sol. Introduction to feedback

Feedback is used in virtually all amplifier systems. Harold black, an electronics engineer with the Western Electric company, invented the feedback amplifier in 1928 while searching for methods to stabilize the gain of amplifiers for use in telephone repeaters.

In a feedback system, a signal that is proportional to the output is fed back to the input and combined with the input signal to produced a desired system response. As we will see, external feedback is used deliberately to achieve particular undesired system response may be produced.

Feedback can be either negative or positive. In negative feedback, a portion of the output signal is subtracted from the input signal; in positive feedback, a portion of the output signal is added to the input signal. Negative feedback, for example tends to maintain a constant value of amplifier voltage gain against variations in transistor parameters, supply Voltage and temperature. Positive feedback is used in the design of oscillators and in a number of other applications.

#### Advantages and Disadvantages of Negative feedback Advantages

**1. Gain sensitivity:** Variations in the circuit transfer function (gain) as a result of changes in transistor parameters are reduced by feedback. This reduction in sensitivity is one of the most attractive features of negative feedback.

**2. Bandwidth extension:** The bandwidth of a circuit that incorporates negative feedback is larger than of the basic amplifier.

**3. Noise sensitivity:** Negative feedback may increase the signal-to -noise ratio if noise is generated within the feedback loop.

**4. Reduction of nonlinear distortion:** Since transistors have nonlinear characteristics, distortion may appear in the input signals, especially at large signal levels, Negative feedback reduces this distortion.

**5. Control of impedance level:** The input an output impedances can be increased or decreased with the proper type of negative feedback.

#### Disadvantages

**1. Circuit gain:** The overall amplifier gain, with negative feedback, is reduced compared to the basic amplifier used in the circuit.

**2. Stability:** There is a possibility that the feedback circuit may become unstable (oscillate) at high frequencies.

\*\*\*\*

### Vision 2021 Batch-3

A Course for ESE & GATE Electronics Aspirants

OUR TOP GRADIANS IN GATE 2020

### Classroom

### Vision 2021-Course for ESE & GATE (Batch-3)

### **Electronics & Communication Engineering**

# Vision 2021 A Course for ESE & GATE Electronics Aspirants Batch-3

### Why take this course?

- > 650+ Hours of Live Classes for ESE & GATE Technical Syllabus

- > 150+ Hours of Live Classes for ESE Prelims Paper 1 Syllabus

- > 750+ Quizzes & Conventional Assignments for Practice

- > Subject & Full-Length Mock Tests for GATE & ESE

MN Ramesh | Rakesh talreja | Chandan Jha | Vijay Bansal

Prep Smart. Score Better. Go gradeup

www.gradeup.co