Time Left - 25:00 mins

GATE EC 2022 National Champion Quiz: Digital Circuits

Attempt now to get your rank among 352 students!

Question 1

In ADC, the full scale input voltage of 9 V with its resolution being 6 mV, then the number of bits used in the ADC _______.

Question 2

The I/P – O/P voltage for the standard TTL family are given by Vohmin = 2.6 V Volmax = 0.6V  = 2V and

= 2V and  = 0.4 V. The maximum – amplitude noise that can be tolerated when a high I/P is driving an input is

= 0.4 V. The maximum – amplitude noise that can be tolerated when a high I/P is driving an input is

Question 3

Which of following logic expression are shown

Question 4

A weighted resistor type digital to analog converter is designed as shown in the figure below. The input voltage is equal to 0 V for logic input ‘0’ and is equal to 5 V for logic input ‘1’. If the resolution of the digital to analog converter is equal to –0.3 V, then the value of RF (in Ω) is equal to

Question 5

What will be the output Y, if the input number  as shown in the below digital circuit?

as shown in the below digital circuit?

Question 6

Consider the following circuit of a synchronous counter,

If the initial state of the counter is ![]() , the clock period is 50 ns, the flip-flips are ideal. Find the MOD number of the counter.

, the clock period is 50 ns, the flip-flips are ideal. Find the MOD number of the counter.

Question 7

Contents of the Accumulator (A) after execution of the following assembly language program of an 8085 microprocessors, is

STC

CMC

MVIA, 55H

MVIB, 25H

ADD B

DAA

HLT

Question 8

Consider the circuit shown in the figure below:

The input to the circuit is two, 2-bit numbers. The numbers are represented as (A1 A0) and (B1B0). The function of the circuit is

Question 9

Let the minimum number of NAND gates required for the implementation of AB+CD is X and the minimum number of nor gates required for the implementation of AB+CD is Y .Then X*Y =_________

Question 10

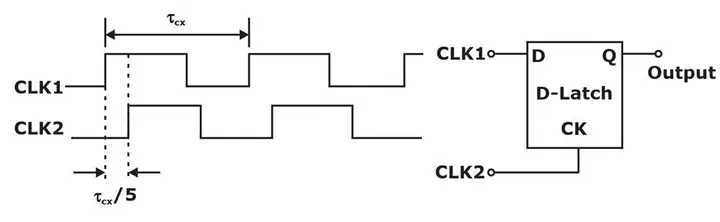

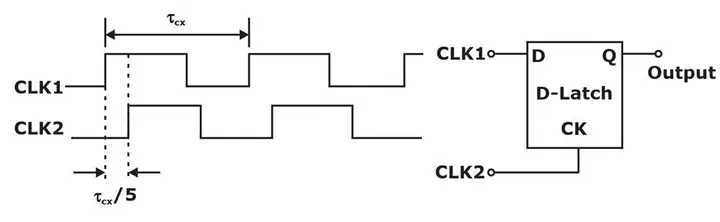

Consider the D-Latch shown in the figure, which is transparent when its clock input CK is high and has zero propagation delay. In the figure, the clock signal CLK1 has a 50% duty cycle and CLK2 is a one-fifth period delayed version of CLK1. The duty cycle at the output latch in percentage is ____.

Question 11

Three memory chips having equal 10 - bits address bus are of sizes 1KB, 2KB and 4KB.The data bus sizes of these three chips respectively

Question 12

Consider an excess-3 to BCD code converter as shown below which accepts excess-3 code as input and outputs corresponding BCD code

The simplified Boolean expression for the output bit Y is

- 352 attempts

- 3 upvotes

- 0 comments

Sep 23ESE & GATE EC